聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602977 -

EPLD

+關(guān)注

關(guān)注

0文章

8瀏覽量

10470 -

可編程邏輯器件

+關(guān)注

關(guān)注

5文章

139瀏覽量

30308

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

#硬聲創(chuàng)作季 #EDA EDA原理及應(yīng)用-03.03 簡(jiǎn)單可編程邏輯器件結(jié)構(gòu)

EDA工具邏輯器件可編程邏輯可編程邏輯器件

水管工

發(fā)布于 :2022年09月24日 23:09:58

電氣安全技術(shù)-1 可編程邏輯器件的結(jié)構(gòu)與表示方法(1)#電氣安全技術(shù)

電氣安全

學(xué)習(xí)電子

發(fā)布于 :2023年03月19日 12:51:08

電氣安全技術(shù)-1 可編程邏輯器件的結(jié)構(gòu)與表示方法(2)#電氣安全技術(shù)

電氣安全

學(xué)習(xí)電子

發(fā)布于 :2023年03月19日 12:51:50

【下載】《從零開始學(xué)CPLD和Verilog HDL編程技術(shù)》

學(xué)會(huì)CPLD的系統(tǒng)設(shè)計(jì)技術(shù)。本書以ALTERA公司的系列芯片為目標(biāo)載體,簡(jiǎn)要分析了可編程邏輯器件的結(jié)構(gòu)和特點(diǎn),以及相應(yīng)開發(fā)軟件的使用方法,同時(shí),還用大量篇幅介紹了初學(xué)者最容易掌握的Verilog

發(fā)表于 03-30 15:07

應(yīng)用CPLD實(shí)現(xiàn)交通控制系統(tǒng)芯片設(shè)計(jì)

介紹可編程邏輯器件的結(jié)構(gòu)和開發(fā)軟件MAX+PLUSII 主要特點(diǎn),以交通控制系統(tǒng)電路芯片設(shè)計(jì)為例, 敘述自頂向下的設(shè)計(jì)方法。

發(fā)表于 04-16 14:14

?26次下載

應(yīng)用CPLD 實(shí)現(xiàn)交通控制系統(tǒng)芯片設(shè)計(jì)

介紹可編程邏輯器件的結(jié)構(gòu)和開發(fā)軟件MAX+PLUSII 主要特點(diǎn),以交通控制系統(tǒng)電路芯片設(shè)計(jì)為例, 敘述自頂向下的設(shè)計(jì)方法。

發(fā)表于 05-14 14:46

?23次下載

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

《可編程邏輯器件基礎(chǔ)及應(yīng)用》是一門側(cè)重掌握可編程邏輯器件的基本結(jié)構(gòu)和原理的課程。重點(diǎn)是使學(xué)生掌握基于可編程

發(fā)表于 03-24 14:22

?29次下載

可編程邏輯器件在高準(zhǔn)確度A/D轉(zhuǎn)換器中的應(yīng)用

【摘 要】 介紹了可編程邏輯器件的結(jié)構(gòu)、優(yōu)點(diǎn),及其在一種高準(zhǔn)確度A/D轉(zhuǎn)換器中的應(yīng)用。設(shè)計(jì)中采用了通用陣列邏輯芯片GAL16V8。

發(fā)表于 05-15 22:30

?1071次閱讀

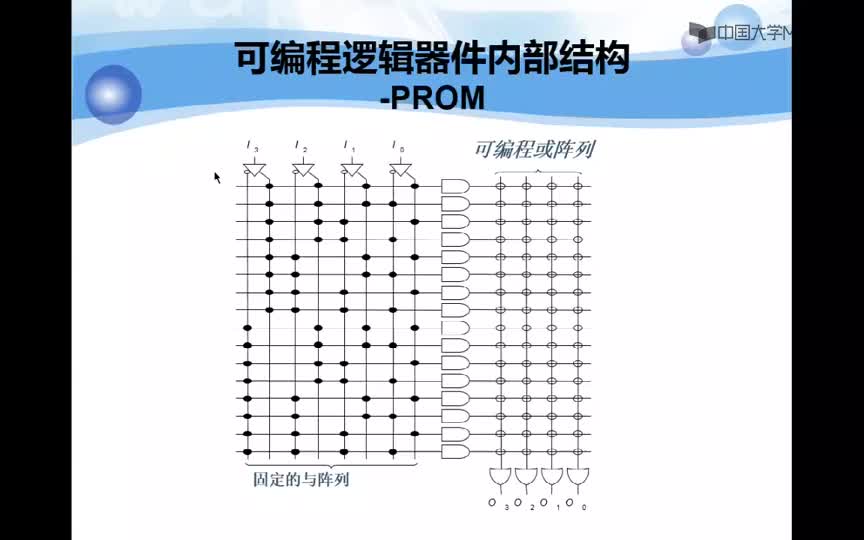

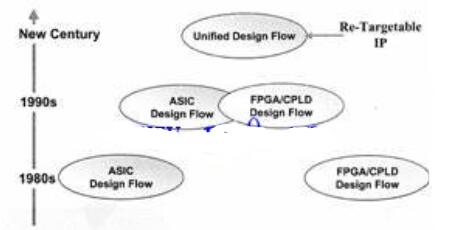

可編程邏輯器件的基本結(jié)構(gòu)及電路表示方法

可編程邏輯器件 (Programmable Logic Device,PLD)起源于20世紀(jì)70年代,是在 專用集成電路 (ASIC)的基礎(chǔ)上發(fā)展起來的一種新型邏輯器件,是當(dāng)今數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件平臺(tái),其主要特點(diǎn)就是完

發(fā)表于 05-30 15:43

?5867次閱讀

可編程邏輯器件的原理與結(jié)構(gòu)說明

隨時(shí)寫入新數(shù)據(jù),但數(shù)據(jù)易失,一旦掉電所存數(shù)據(jù)全部丟失。只讀存儲(chǔ)器(ROM)的內(nèi)容只能讀出不能寫入,存儲(chǔ)的數(shù)據(jù)不會(huì)因斷電而消失,所以具有非易失性。固定ROM是由地址譯碼器和存儲(chǔ)矩陣構(gòu)成的組合邏輯電路。

發(fā)表于 05-28 16:22

?4373次閱讀

可編程邏輯器件的分類有哪些

可編程邏輯器件(PLD)是20世紀(jì)70年代發(fā)展起來的一種新型邏輯器件,是目前數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件基礎(chǔ)。根據(jù)可編程邏輯器件結(jié)構(gòu)、集成度以及

發(fā)表于 06-10 17:52

?2.9w次閱讀

采用編程邏輯器件控制8個(gè)LED小燈電路的設(shè)計(jì)

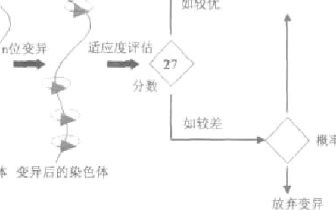

演化硬件(EHW)是指能根據(jù)外部環(huán)境變化自動(dòng)改變自身結(jié)構(gòu)和功能的一類硬件,它把可編程邏輯器件的結(jié)構(gòu)位串當(dāng)作染色體,通過演化算法進(jìn)行搜索,用符合要求的染色體配置可編程邏輯器件,得到要設(shè)計(jì)

發(fā)表于 08-03 17:35

?2514次閱讀

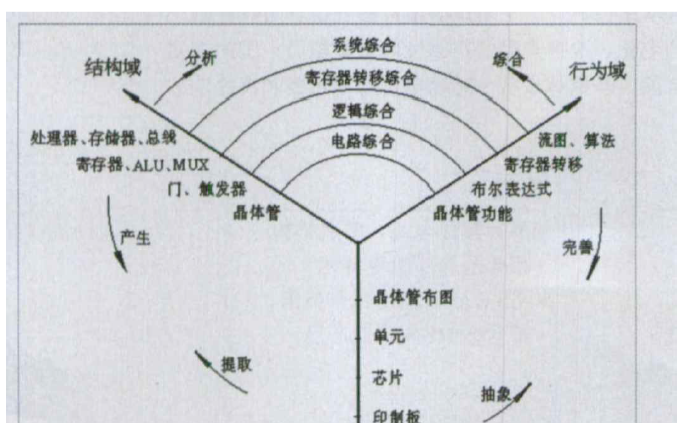

FPGA可編程邏輯器件的原理和結(jié)構(gòu)與描述語言

效字信號(hào)在時(shí)間上和數(shù)值上都是一些離散的數(shù)值,在電路中常表現(xiàn)為突變的電壓或電流:數(shù)字倍號(hào)是種二值信號(hào),用兩個(gè)電平(高電平和低電平)來分別示兩個(gè)邏輯值(邏輯1和邏輯0)。在正邏輯中,用1代

發(fā)表于 01-20 15:49

?11次下載

可編程邏輯器件的結(jié)構(gòu)

可編程邏輯器件的結(jié)構(gòu)

評(píng)論