審核編輯黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

-

電路設計

+關注

關注

6673文章

2451瀏覽量

204153 -

信號完整性

+關注

關注

68文章

1404瀏覽量

95458 -

emc

+關注

關注

170文章

3914瀏覽量

183119 -

高速電路

+關注

關注

8文章

157瀏覽量

24240

發(fā)布評論請先 登錄

相關推薦

【下載】《信號完整性分析》

省部級獎勵10項。在IEEE Trans.上發(fā)表長文12篇;正式出版教材/專著/譯著12部。研究方向:高速電路設計與信號完整性分析,EDA技術及軟件研發(fā)。目錄第1章

發(fā)表于 09-19 18:21

【資料】超高速數據采集系統(tǒng)的時序設計與信號完整性分析_黃春行

`本文首先介紹了信號完整性分析的基本概念和仿真模型,然后闡述了一個具體的超高速數據采集系統(tǒng)的框架,原理和實現方案.`

發(fā)表于 03-30 11:04

高速電路信號完整性分析與設計—高速信號完整性的基本理論

2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而

發(fā)表于 05-25 16:21

?1743次閱讀

高速電路信號完整性分析與設計—電源完整性分析

在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SISignal Integrity)和電源完整性 (PIPower Int

發(fā)表于 05-29 13:51

?2702次閱讀

超高速數據采集系統(tǒng)的時序設計與信號完整性分析

電子發(fā)燒友網站提供《超高速數據采集系統(tǒng)的時序設計與信號完整性分析.pdf》資料免費下載

發(fā)表于 09-20 11:34

?0次下載

高速電路設計與信號完整性分析

隨著電子系統(tǒng)和高集成度芯片向高速度、高密度、大功耗、低電壓、大電流的趨勢發(fā)展,電路中的信號完整性問題日益嚴重。信號失真、定時錯誤和不正確的數

發(fā)表于 09-25 14:46

?0次下載

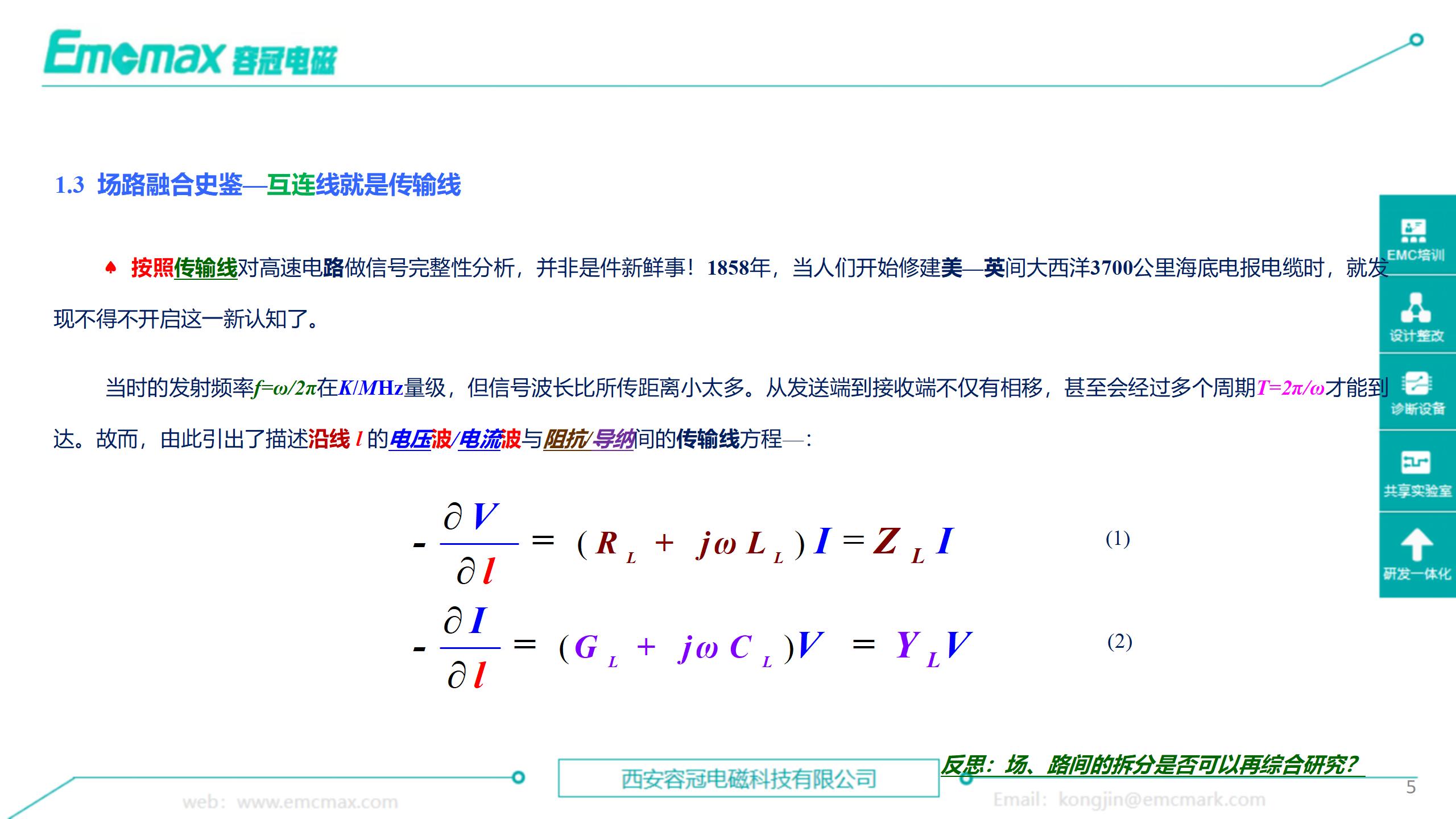

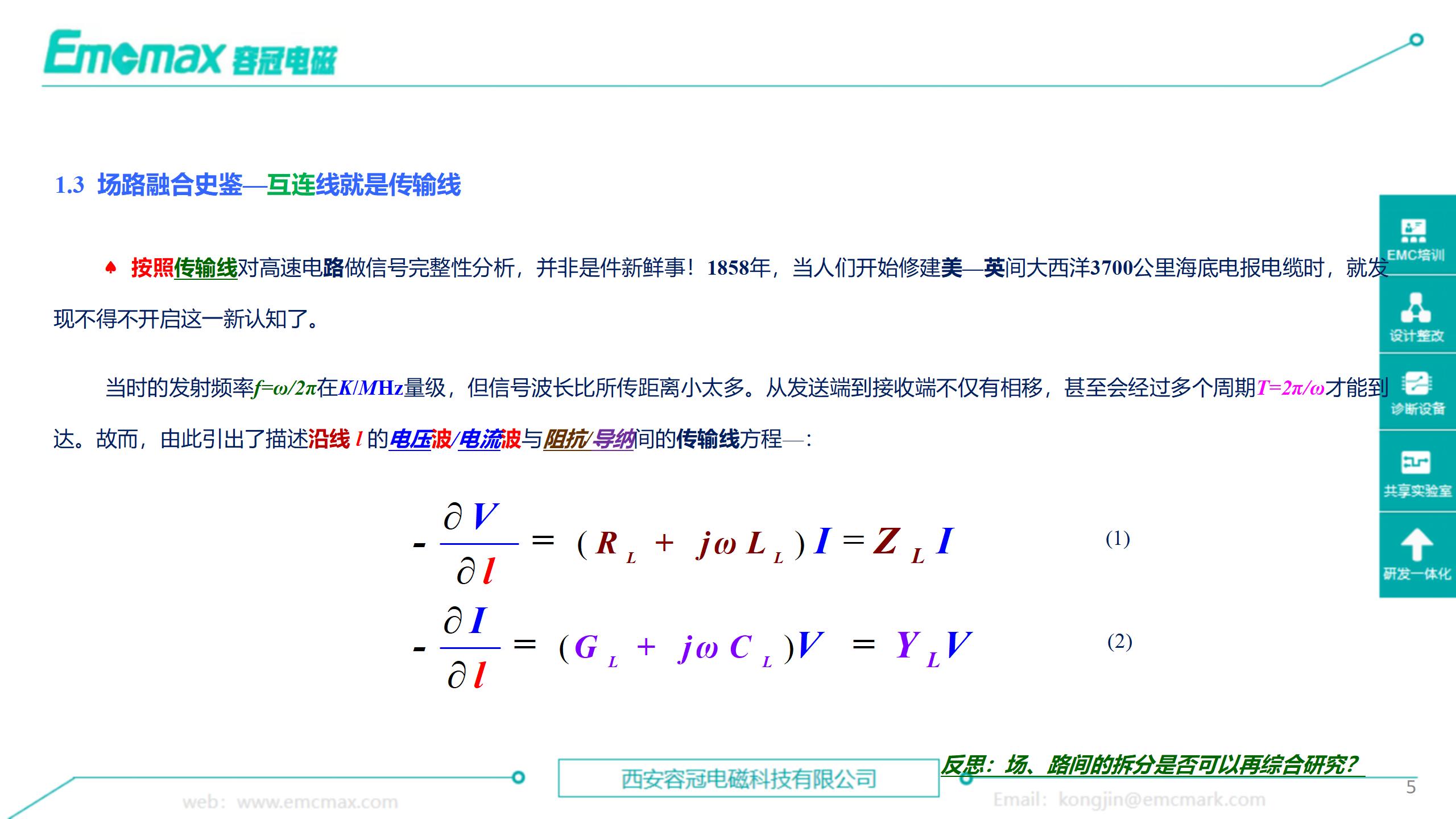

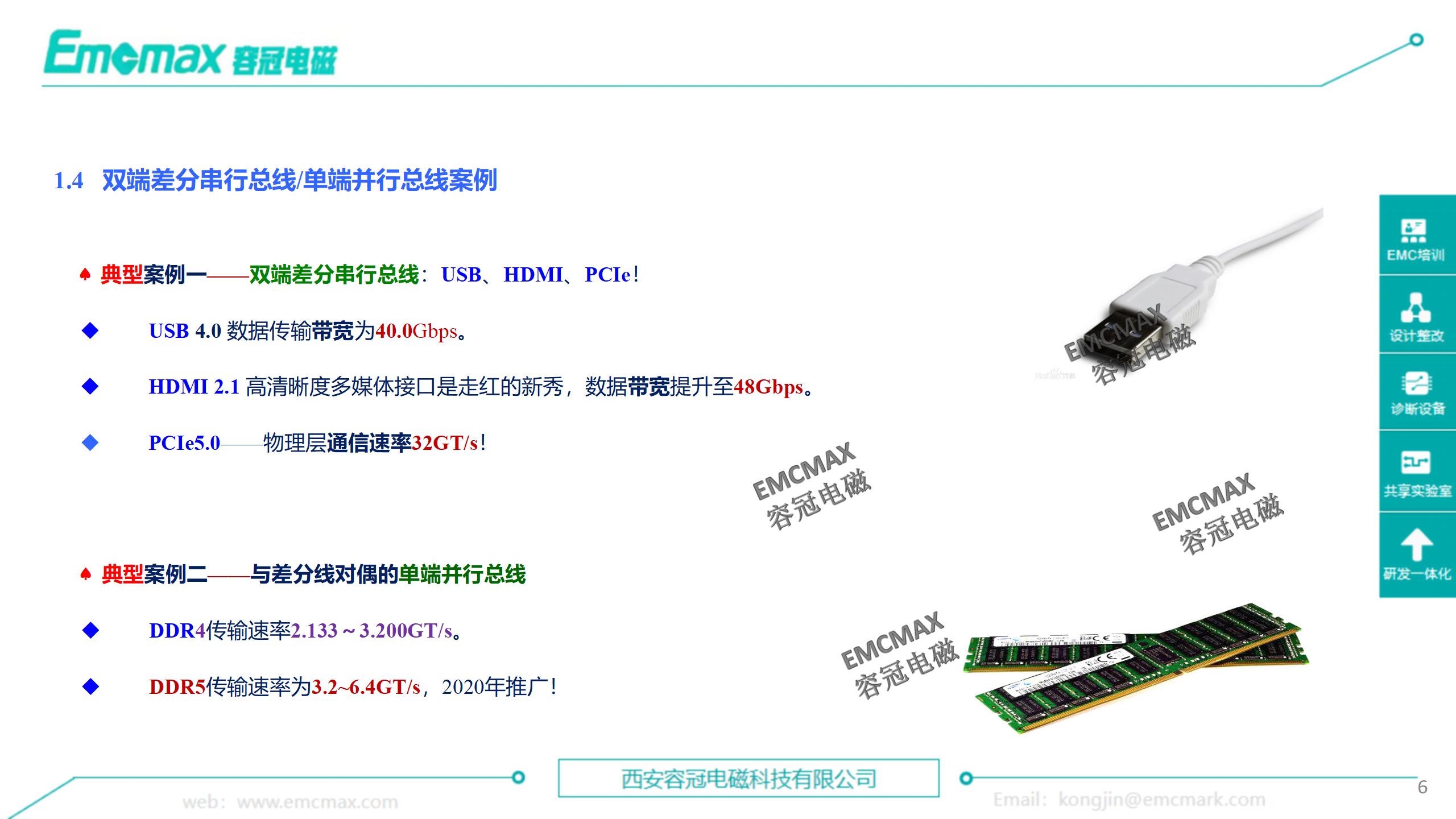

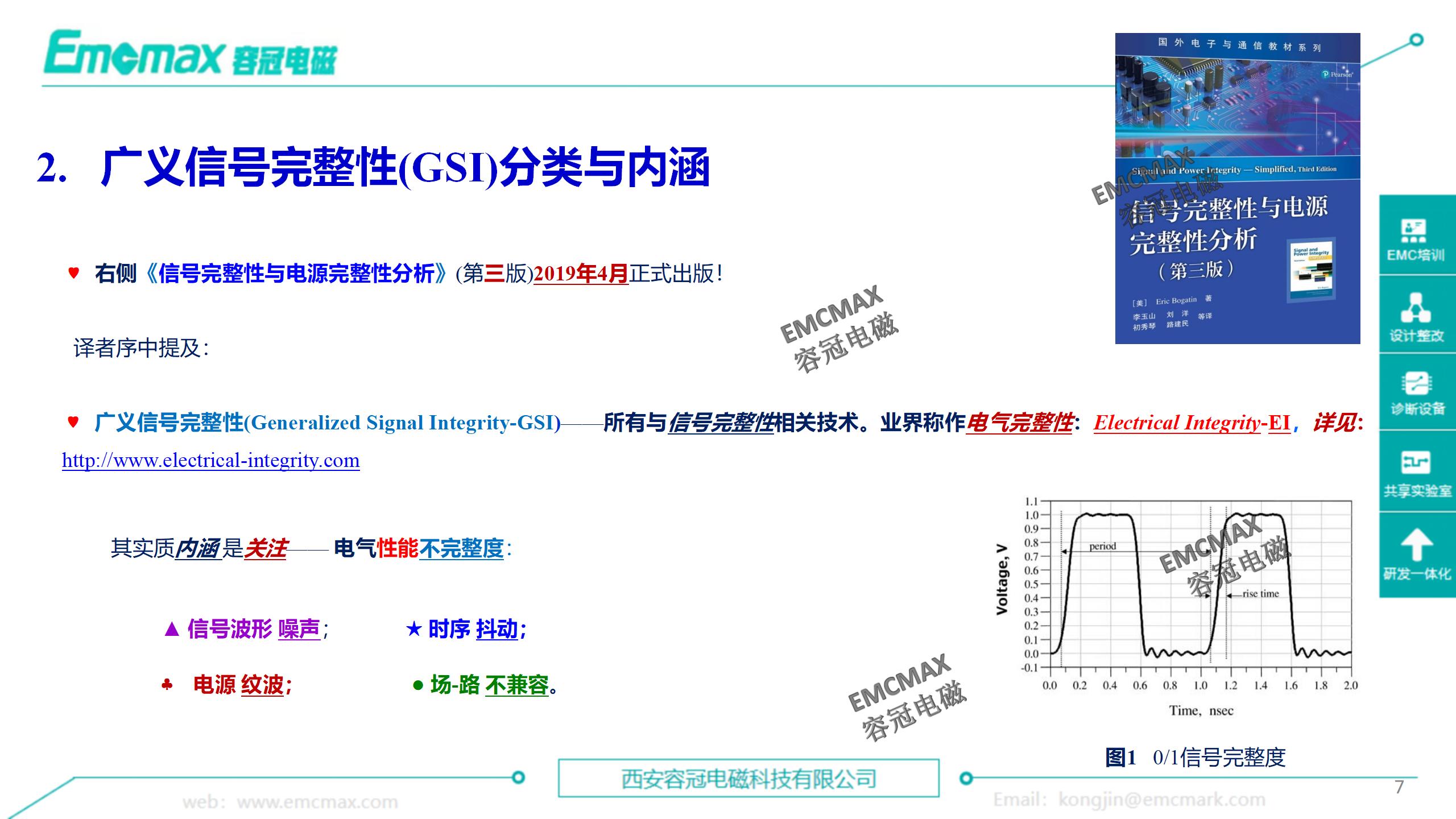

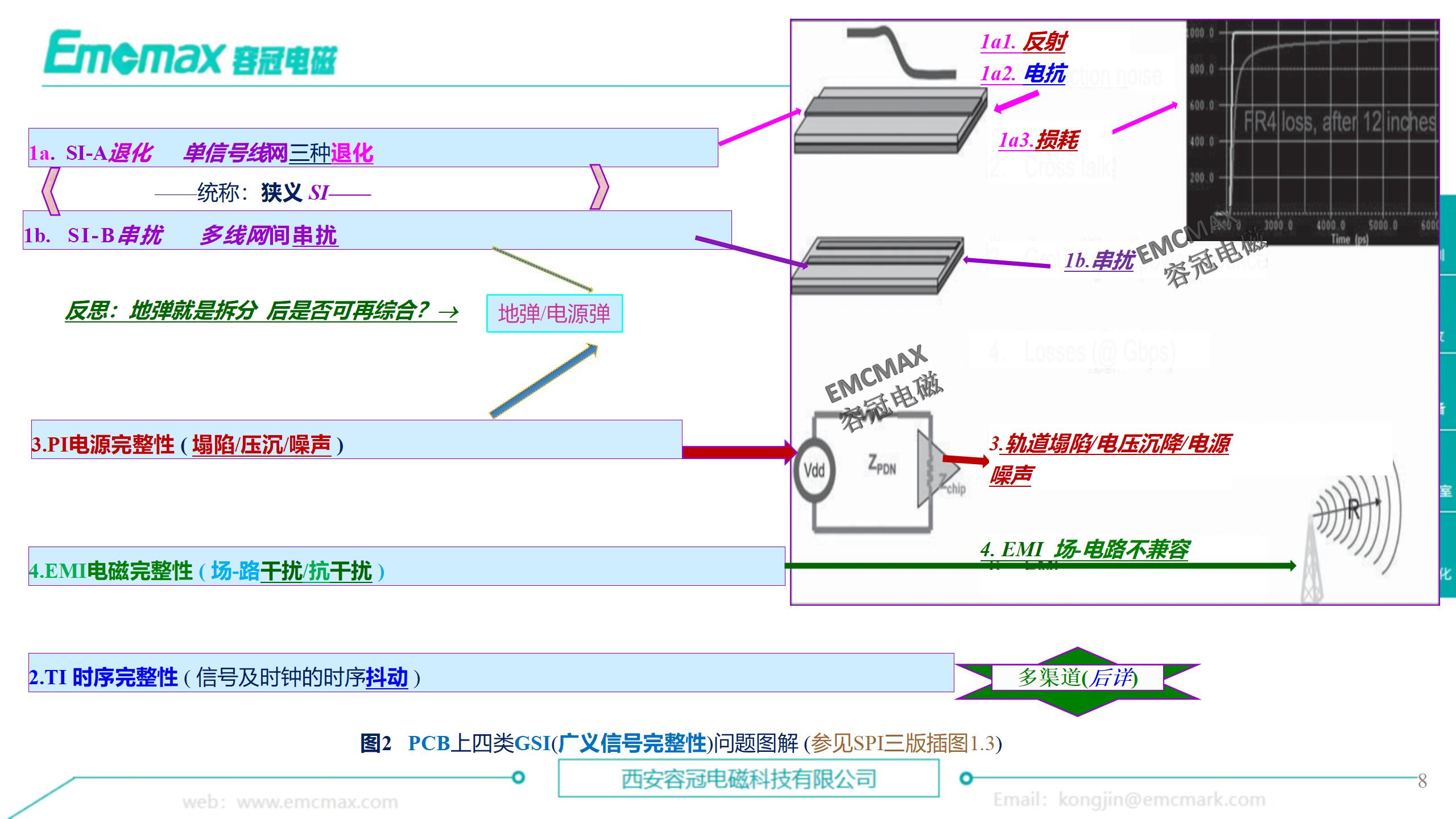

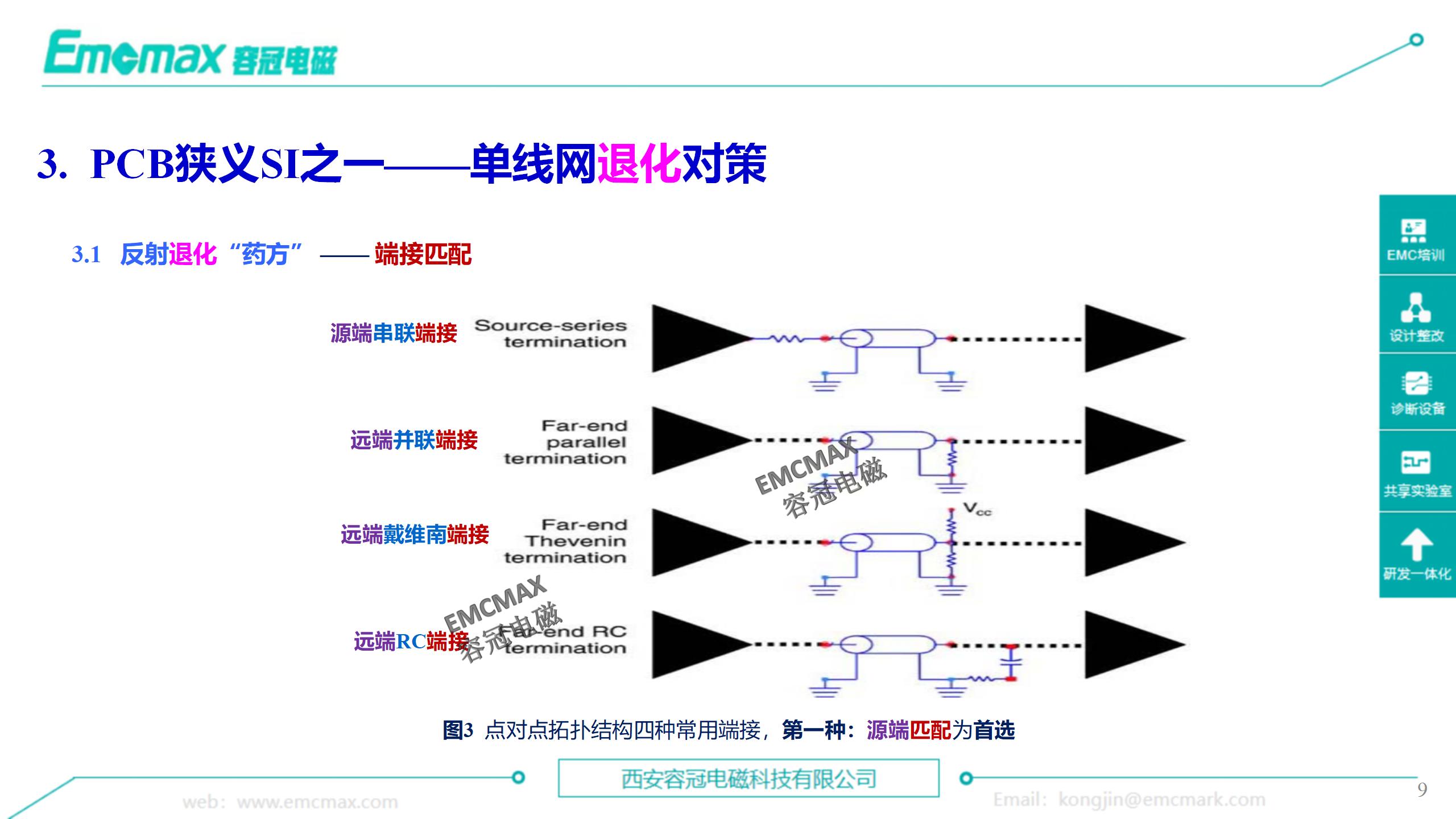

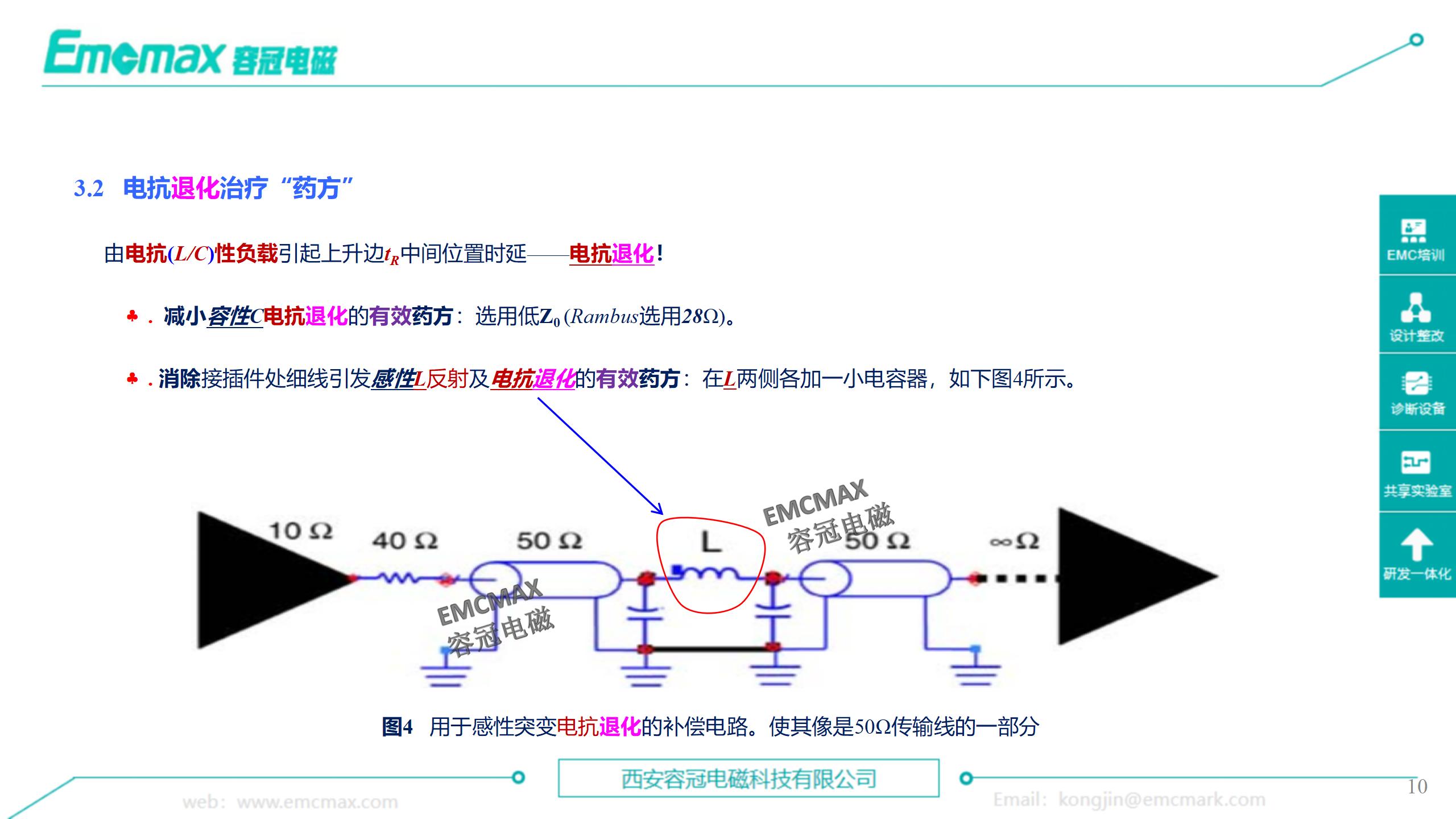

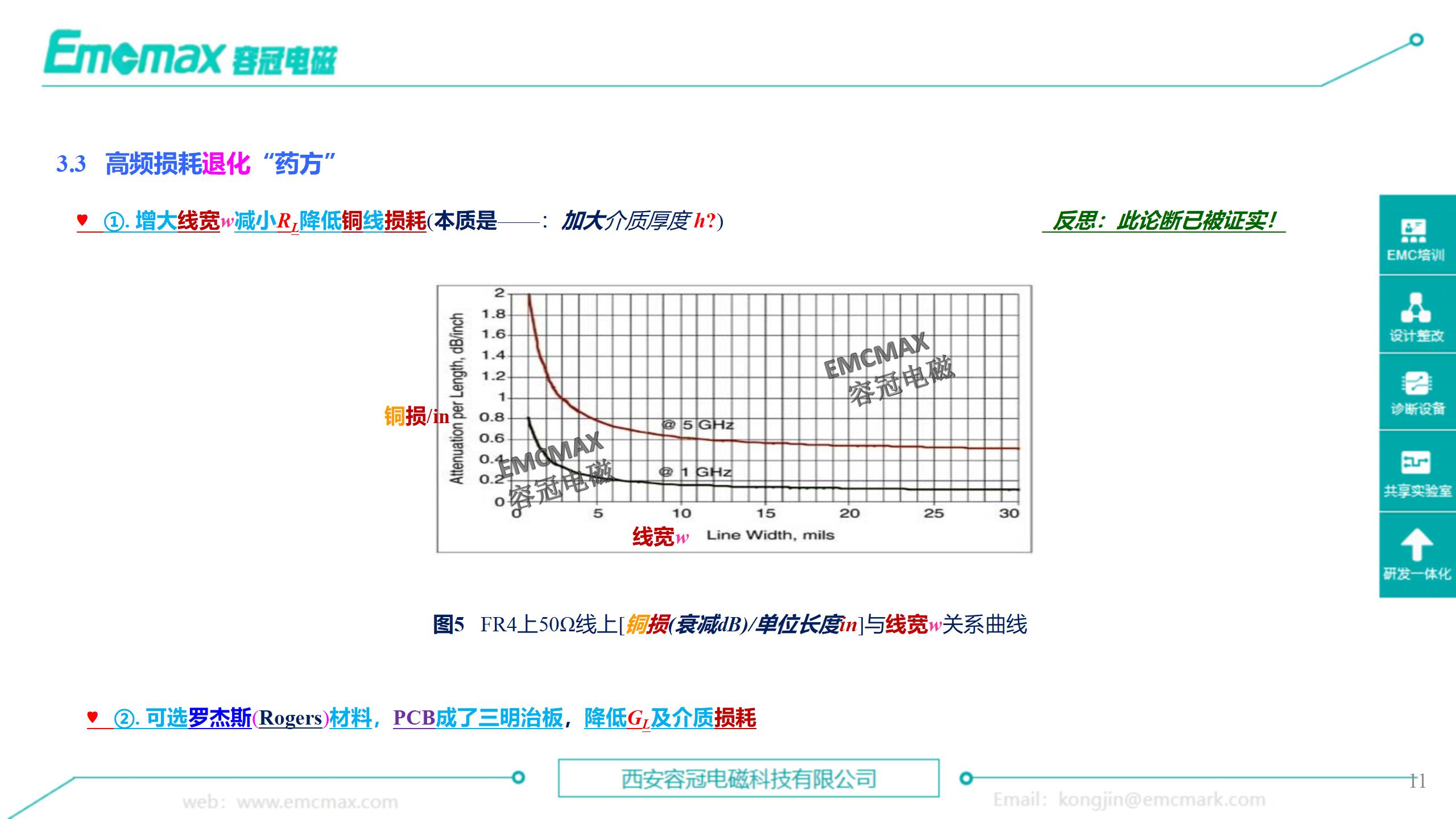

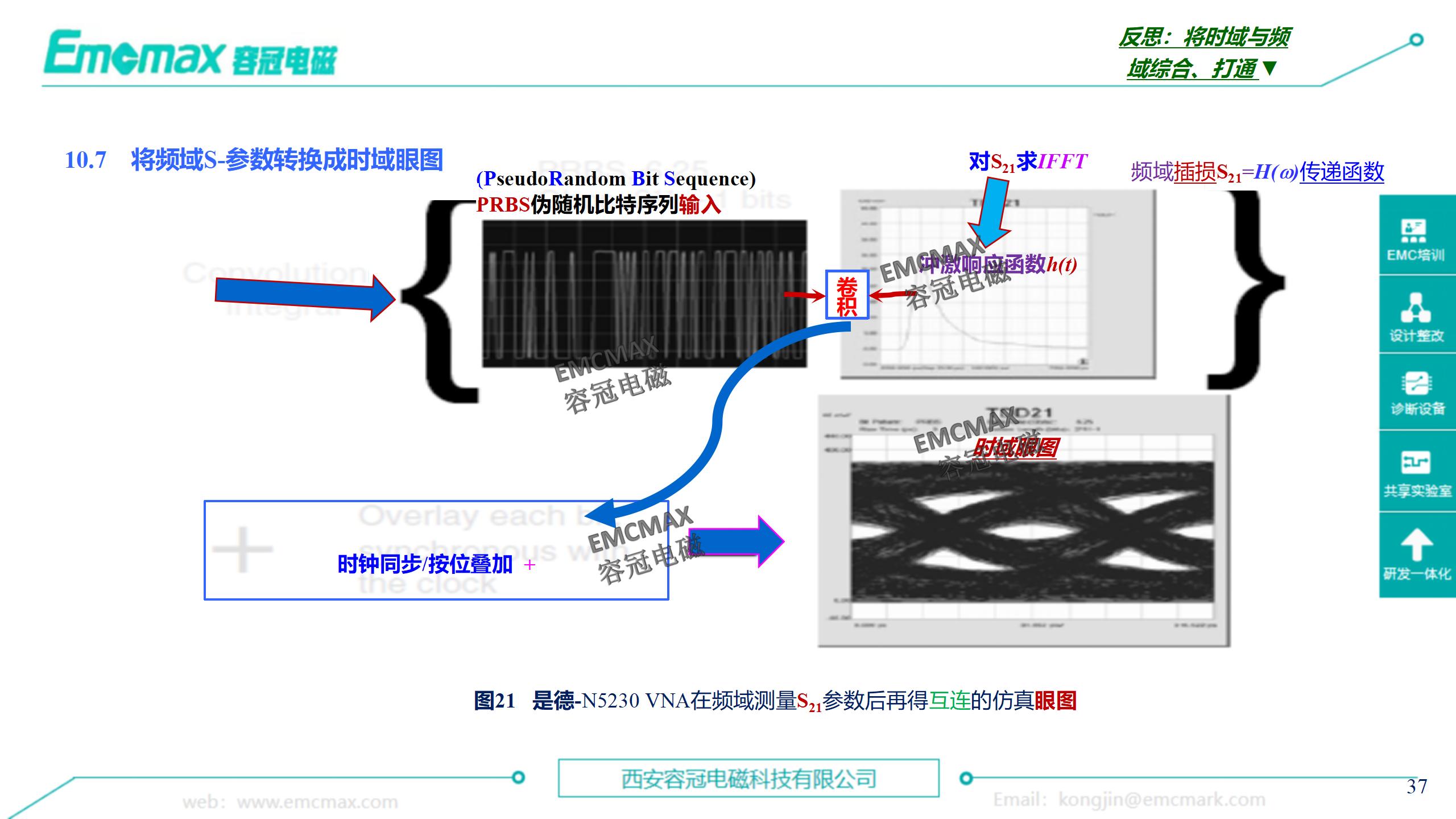

超高速電路設計面臨的挑戰(zhàn)與廣義信號完整性(GSI)內涵和走勢

超高速電路設計面臨的挑戰(zhàn)與廣義信號完整性(GSI)內涵和走勢

評論