Intel公司的Stratix 10 GXFPGA和SX SoC系列產(chǎn)品比前一代產(chǎn)品成本提供2X性能和高達(dá)70低功耗,具有幾個(gè)開創(chuàng)性的創(chuàng)新如所有新型HyperFlex?和架構(gòu),能滿足日益增長(zhǎng)的帶寬和處理性能,而滿足功率預(yù)算.嵌入硬件系統(tǒng)基于四核64位ARM?Cortex?-A53,采用Intel 14-nm Tri-Gate (FinFET)技術(shù)和混合性3D片上系統(tǒng)(SiP)技術(shù),單片核多達(dá)550萬(wàn)和邏輯單元,多達(dá)96個(gè)全雙工收發(fā)器,數(shù)據(jù)速率高達(dá)28.3Gbps,主要用在計(jì)算和存儲(chǔ),網(wǎng)絡(luò)設(shè)備,光傳輸網(wǎng)絡(luò),廣播,軍用雷達(dá),醫(yī)療設(shè)備,測(cè)試和測(cè)量以及5G無(wú)線設(shè)備,ASIC原型.本文介紹了Intel Stratix 10 GXFPGA和SoC器件主要特性,架構(gòu)框圖以及Intel? Stratix? 10 GX FPGA 開發(fā)板主要特性和詳細(xì)電路圖.

Intel’s 14-nm Intel? Stratix? 10 GX FPGAs and SX SoCs deliver 2X the coreperformance and up to 70% lower power over previous generation high-performanceFPGAs.Featuring several groundbreaking innovations, including the all new HyperFlex? core architecture, this device family enables you to meet the demand for ever-increasing bandwidth and processing performance in your most advanced applications, while meeting your power budget.

With an embedded hard processor system (HPS) based on a quad-core 64-bit ARM? Cortex?-A53, the Intel Stratix 10 SoC devices deliver power efficient,application-class processing and allow designers to extend hardware virtualization into the FPGA fabric. Intel Stratix 10 SoC devices demonstrate Intel’s commitment to high-performance SoCs and extend Intel’s leadership in programmable devices featuring an ARM-based processor system.

Important innovations in Intel Stratix 10 FPGAs and SoCs include:

? All new HyperFlex core architecture delivering 2X the core performance comparedto previous generation high-performance FPGAs

? Industry leading Intel 14-nm Tri-Gate (FinFET) technology

? Heterogeneous 3D System-in-Package (SiP) technology

? Monolithic core fabric with up to 5.5 million logic elements (LEs)

? Up to 96 full duplex transceiver channels on heterogeneous 3D SiP transceivertiles

? Transceiver data rates up to 28.3 Gbps chip-to-chip/module and backplaneperformance

? M20K (20 kbit) internal SRAM memory blocks

? Fractional synthesis and ultra-low jitter LC tank based transmit phase locked loops(PLLs)

? Hard PCI Express? Gen3 x16 intellectual property (IP) blocks

? Hard 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC) in everytransceiver channel

? Hard memory controllers and PHY supporting DDR4 rates up to 2666 Mbps per pin

? Hard fixed-point and IEEE 754 compliant hard floating-point variable precisiondigital signal processing (DSP) blocks with up to 10 TFLOPS compute performancewith a power efficiency of 80 GFLOPS per Watt

? Quad-core 64-bit ARM Cortex-A53 embedded processor running up to 1.5 GHz inSoC family variants

? Programmable clock tree synthesis for flexible, low power, low skew clock trees

? Dedicated secure device manager (SDM) for:

— Enhanced device configuration and security

— AES-256, SHA-256/384 and ECDSA-256/384 encrypt/decrypt accelerators and

authentication

— Multi-factor authentication

— Physically Unclonable Function (PUF) service and software programmabledevice configuration capability

? Comprehensive set of advanced power saving features delivering up to 70% lowerpower compared to previous generation high-performance FPGAs

? Non-destructive register state readback and writeback, to support ASICprototyping and other applications.

With these capabilities, Intel Stratix 10 FPGAs and SoCs are ideally suited for the most demanding applications in diverse markets such as:

? Compute and Storage—for custom servers, cloud computing and data centeracceleration

? Networking—for Terabit, 400G and multi-100G bridging, aggregation, packetprocessing and traffic management

? Optical Transport Networks—for OTU4, 2xOTU4, 4xOTU4

? Broadcast—for high-end studio distribution, headend encoding/decoding, edgequadrature amplitude modulation (QAM)

? Military—for radar, electronic warfare, and secure communications

? Medical—for diagnostic scanners and diagnostic imaging

? Test and Measurement—for protocol and application testers

? Wireless—for next-generation 5G networks

? ASIC Prototyping—for designs that require the largest monolithic FPGA fabricwith the highest I/O count

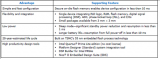

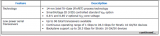

Intel Stratix 10 GXFPGA和SoC器件主要特性:

?

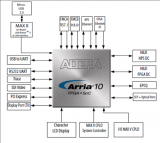

圖1.Intel Stratix 10 GXFPGA和SoC架構(gòu)框圖

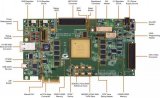

Intel? Stratix? 10 GX FPGA 開發(fā)板

The new Intel Quartus? Prime Design Suite design software includes everythingneeded to design for Intel FPGAs, SoCs and CPLDs from design entry and synthesis tooptimization, verification and simulation. The Intel Quartus Prime Design Suitesoftware includes an additional Spectra-Q? engine that is optimized for future devices.

The Spectra-Q engine enables new levels of design productivity for next generation programmable devices with a set of faster and more scalable algorithms, a hierarchical database infrastructure and a unified compiler technology.

The Intel Quartus Prime Design Suite software is available in three editions based on specific design requirements: Pro, Standard, and Lite Edition. The Intel Stratix 10FPGA Development Kit is supported by the Intel Quartus Prime Pro Edition.

Intel Quartus Prime Pro Edition: The Intel Quartus Prime Pro Edition is optimized tosupport the advanced features in Intel’s next generation FPGAs and SoCs, startingwith the Intel Arria? 10 device family and requires a paid license.

Included in the Intel Quartus Prime Pro Edition are the Intel Quartus Prime software,Nios? II EDS and the MegaCore IP Library. To install Intel’s development tools,download the Intel Quartus Prime Pro Edition software from the Intel Quartus PrimePro Edition page in the Download Center of Intel’s website.

圖2.Intel? Stratix? 10 GX FPGA 開發(fā)板外形圖(正面)

圖3.Intel? Stratix? 10 GX FPGA 開發(fā)板外形圖(背面)

圖4.Intel? Stratix? 10 GX FPGA 開發(fā)板框圖

圖5.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(1)

圖6.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(2)

圖7.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(3)

圖8.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(4)

圖9.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(5)

圖10.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(6)

圖11.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(7)

圖12.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(8)

圖13.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(9)

圖14.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(10)

圖15.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(11)

圖16.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(12)

圖17.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(13)

圖18.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(14)

圖19.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(15)

圖20.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(16)

圖21.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(17)

圖22.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(18)

圖23.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(19)

圖24.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(20)

圖25.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(21)

圖26.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(22)

圖27.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(23)

圖28.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(24)

圖29.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(25)

圖30.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(26)

圖31.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(27)

圖32.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(28)

圖33.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(29)

圖34.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(30)

圖35.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(31)

圖36.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(32)

圖37.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(33)

圖38.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(34)

圖39.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(35)

圖40.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(36)

圖41.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(37)

圖42.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(38)

圖43.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(39)

圖44.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(40)

圖45.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(41)

圖46.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(42)

圖47.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(43)

圖48.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(44)

圖49.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(45)

圖50.Intel? Stratix? 10 GX FPGA開發(fā)板電路圖(46)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論